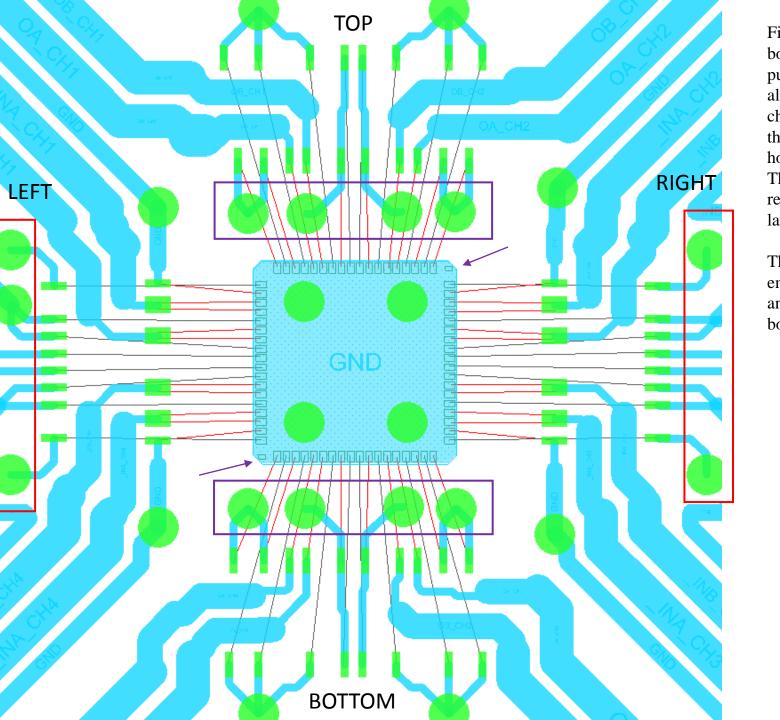

First the board is oriented with the component-side upwards. Then board must be oriented so that the set of four vias, denoted by the purple boxes, are on the top and bottom edges. The chip must be aligned with the board so that the two tabs on opposite corners of the chip are on the top right and bottom left of the chip, as denoted by the purple arrows. The chip is not symmetric about the vertical and horizontal axes, so there is a distinction between the top and bottom. The left side of the board is denoted by three vias that line up (see red boxes) while on the right side only two vias line up by the outer layer of pads.

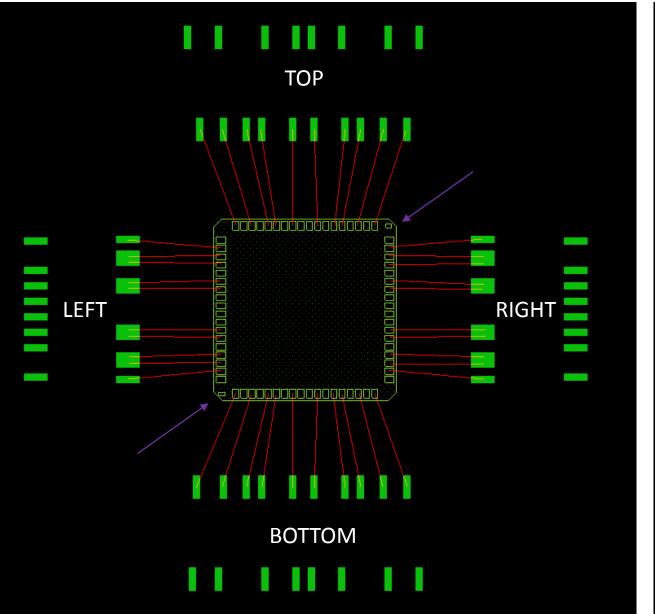

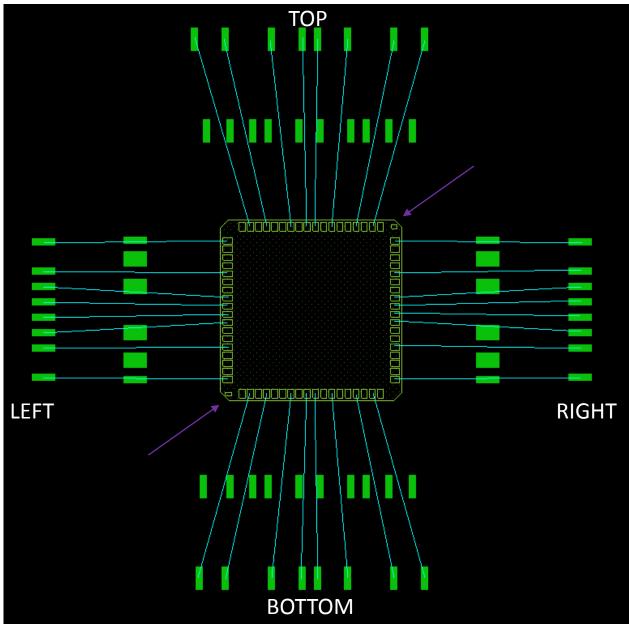

The second picture is a simplified view of the chip and pads to emphasize the wire bonding pattern. Note the tabs in the top-right and bottom-left signify the orientation of the chip relative to the bond pads, as in the diagram to the left.

Wire Bond Diagrams depicting the inner layer bond pad wirings to the left, and the outer layer bond pad wirings to the right.

FASTAMP CHIP

ENN 2017

## LEFT

SWB\_left rtn1\_ch1 inal\_chl ina2\_ch1 rtn2\_ch1 inb1\_ch1 inb2\_ch1 rtn3\_eh1 v300m\_ch1 v300m\_ch4 rtn3\_ch4 inb2\_ch4 inb1\_ch4 rtn2\_ch4 ina2\_ch4 ina1\_ch4 rtn1\_ch4 SW1

## RIGHT

SWB\_right rtn1\_ch2 inal\_ch2 ina2\_ch2 rtn2\_ch2 inb1\_ch2 inb2\_ch2 rtn3\_ch2 v300m\_eh2 v300m\_ch3 rtn3\_ch3 inb2\_ch3 inb1\_ch3 rtn2\_ch3 ina2\_ch3 ina1\_ch3 rtn1\_ch3 SW2

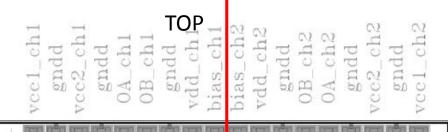

vcc1\_ch4

gndd

vcc2\_ch4

gndd

OA\_ch4

MOLLO9B\_ch4

bias\_ch3

vdd\_ch3

vdd\_ch3

oB\_ch3

oA\_ch3

gndd

vec2\_ch3

gndd

vec2\_ch3

gndd

vcc2\_ch3