# G10 Carrier Board for RMD 8x8 mm<sup>2</sup> APDs

B. Harrop, K. McDonald, M. Newcomer

Apr. 6, 2017

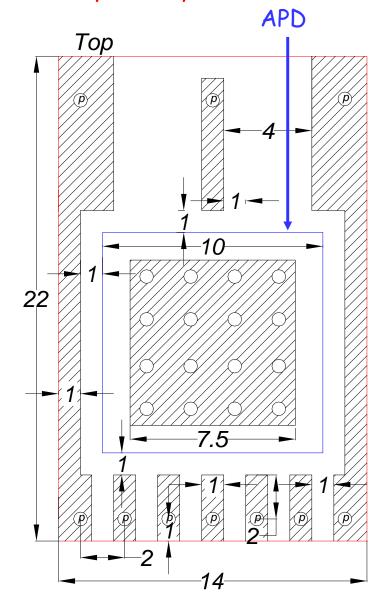

First try at a layout, 3/22/17:

G10 carrier board is 14x22 mm<sup>2</sup>.

APDs have 10x10 mm<sup>2</sup> total area, mounted on the top of the carrier board.

APD bottom contact is 7.5x7.5 mm<sup>2</sup>.

All vias are plated thru, and have pins, soldered on the bottom side.

Wire bonds connect the HV and S (signal) solder pads to the APD.

The HV pad, and the HV wire bond, are encased in conformal coating, on both top and bottom of the carrier board.

#### Pins and Sockets

Better to have sockets on the carrier board, pins on the preamp board. (Repair of a pin easier on a board without an APD.)

Pins could be Mill-Max 5063-0-00-15-00-33-0 "nail head" type, 0.020" pin diameter. <a href="https://www.mill-max.com/assets/new\_products/PCB%20Pins.pdf">https://www.mill-max.com/assets/new\_products/PCB%20Pins.pdf</a>

Sockets could be Mill-Max 1407-0-15-15-11-27-10-0, mounted with the pin hole on the bottom of the carrier board.

https://www.mill-max.com/assets/pdfs/153-201.pdf

Wire bonds will be made to the flat end of the socket. 5063 1407 5063-0-00-XX-00-00-33-0 #11 CONTACT #11 CONTACT 1407-0-15-XX-11-XX-10-0 5 older mount in .024 mounting hole FOR .015"-.020" DIAMETER PINS ( $\delta$  = .003) Solder mount in .040 min. mounting hole 3-FINGER, GROUP A (See page 248) .012 CONTACT PRESS-FIT - INSERTION FORCE 2nd CYCLE INTO SHELL .036 DIA. --- EXTRACTION FORCE SHOULDER PREFERRED .055 DIA. TO ASSIST **CONTACT MATERIAL** ASSEMBLY BERYLLIUM COPPER .083 Alloy 172, MINIMIIM .020 DIA. **Heat Treated** .172DIAMETER PRECISION MACHINED SHELL (CUSTOM DESIGNS WELCOME) MATING PIN DIAMETER (inches ORDER CODE: XXXX - X - XX - XX - XX - XX - XX - 0 **SPECIFICATIONS:** ORDER CODE: XXXX - X - 00 - XX - 00 - 00 - XX - 0 SPECIFICATIONS: **BASIC PART #** Shell Material: Brass Alloy 360, 1/2 Hard Pin Material: Brass Allov 360, 1/2 Hard SPECIFY SHELL FINISH: SPECIFY CONTACT FINISH: (Except where noted) Contact Material: Beryllium Copper Alloy 172, HT BASIC PART # SPECIFY PIN FINISH: 01 200 μ" TIN/LEAD OVER NICKEL 02 100 μ" TIN/LEAD OVER NICKEL 01 200 μ" TIN/LEAD OVER NICKEL 84 100 μ" TIN OVER NICKEL (RoHS) Dimensions: Inches Dimensions: Inches 80 200 μ" TIN OVER NICKEL (RoHS) ◆ 80 200 µ" TIN OVER NICKEL (RoHS) 15 10 μ" GOLD OVER NICKEL (RoHS) 27 30 μ" GOLD OVER NICKEL (RoHS) Tolerances On: Lengths: ±.005 Tolerances On: Lengths: ±.005 15 10 μ" GOLD OVER NICKEL (RoHS) SELECT CONTACT: Diameters: ±.002 Diameters: ±.002 21 20 μ" GOLD OVER NICKEL (RoHS) #11 or #21 CONTACT (DATA ON PAGE 251) Angles: ±2° Angles: ±2° ◆ 34 50 µ" GOLD OVER NICKEL (RoHS) (For alternate contact choices, see group A on page 248)

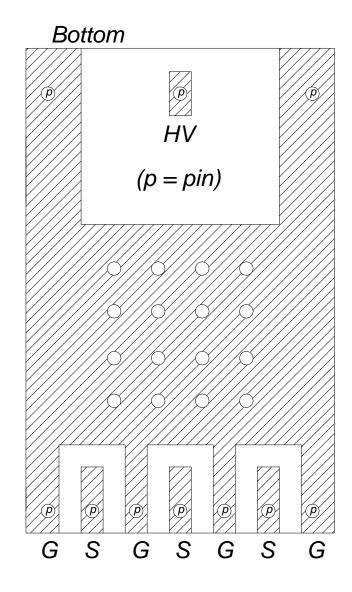

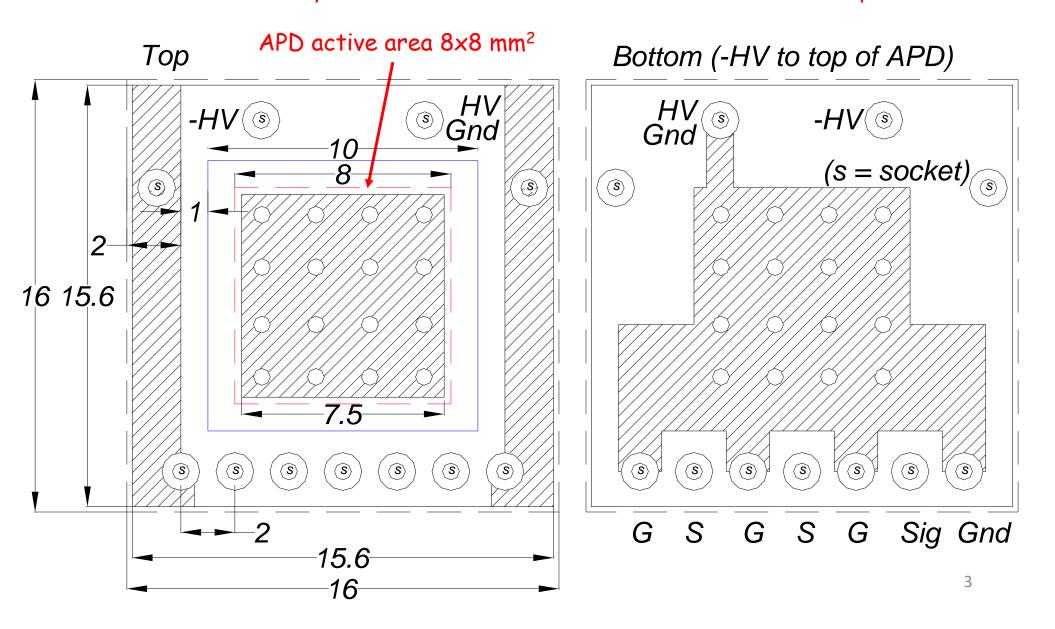

#### Carrier Board Sized for Tiling

The active area of an APD is 8x8 mm<sup>2</sup>.

So, to make a square tiling of such APDs, they could be on a carrier board that is  $16 \times 16 \text{ mm}^2$ , with 25% active area per layer of tiling, and 4 tiling layers for 100% active area. The carrier board is actually  $15.6 \times 15.6 \text{ mm}^2$ , with the APD mounted on its top.

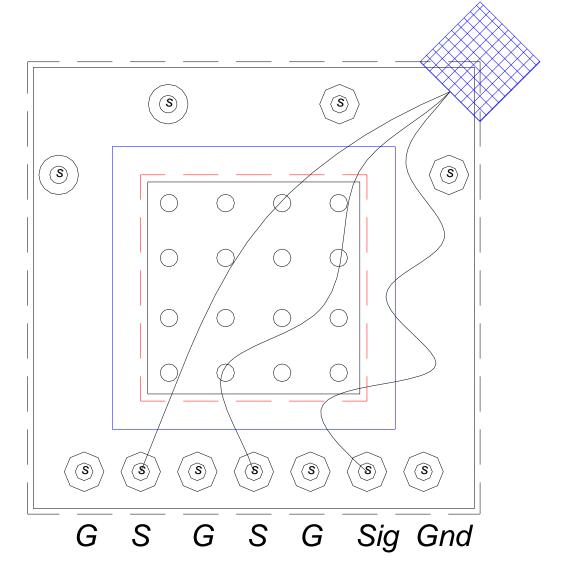

# Tiling, II

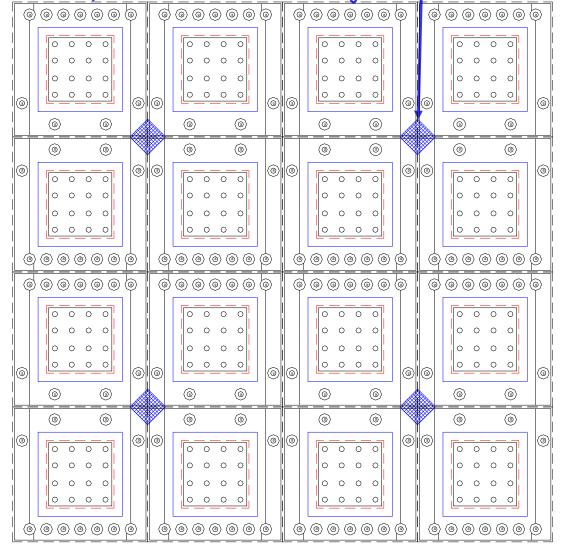

Example of a single tile layer of  $4 \times 4$  carrier boards.

The eventual 4-ch Penn preamp ASIC will be 3x3 mm<sup>2</sup> (shown in blue below), and would be located (on a large readout board) at the corners of 4 adjacent carrier boards.

4 tiling layers, with offsets of 8 mm, achieve 100% coverage.

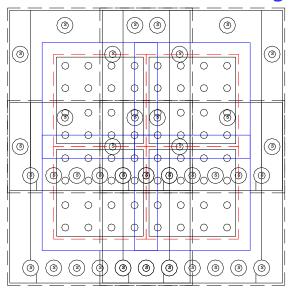

Back View (back of PCB)

Readout/HV/PWR

Amplifier Signal Routed out on back

The next iteration of the surface-mount Penn preamps could be laid in a similar array.

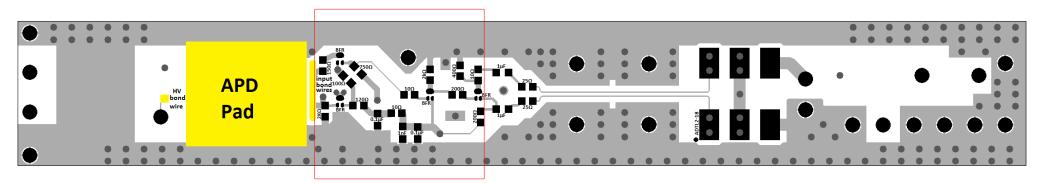

#### Next Surface-Mount Preamp

The present Penn preamp is shown below, together with an indication of the  $16 \times 16 \text{ mm}^2$  footprint of the proposed carrier board.

16x16 mm² footprint of proposed carrier board

The surface-mount components of the preamp should be rearranged to fit within this footprint on bottom side of the preamp board, with the HV connection (and the sockets for the pins of the carrier board) on the top side.

The low-voltage power conditioning, and the signal and HV connectors, will be outside the footprint of the preamp itself, as on the present board. This items should be on the top side of the new preamp to facilitate stacking of the preamp + APD units into a relatively compact 4-layer detector.

The new preamp will include diode protection, and a test-pulse input.

# Option for +HV on the APD Bottom Side

The present scenario uses -HV on the top side of the APD, with the bottom side at ground.

Then, the mesh signal and the signal from the bottom side can both be read out directly, without coupling capacitors.

Alternatively, +HV could be applied to the bottom side of the APD, with the top side at ground.

Bottom (+HV to bottom of APD)

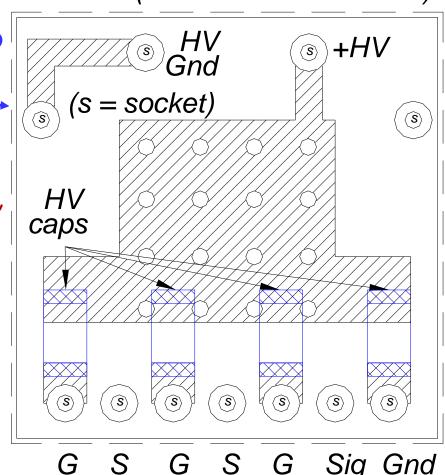

Bottom of carrier board with +HV to the APD bottom side:

This requires that the signal from the bottom side be read out via coupling capacitors (Vishay VJ120-Y-500-M-X shown), which will slightly increase the signal rise time,  $\Rightarrow$  slightly worse time resolution.

The perceived advantage is that the mesh and the APD top are both at ground, which reduces risk of HV breakdown here.

As this seems to be a non-issue, we are NOT in favor of the +HV scenario.

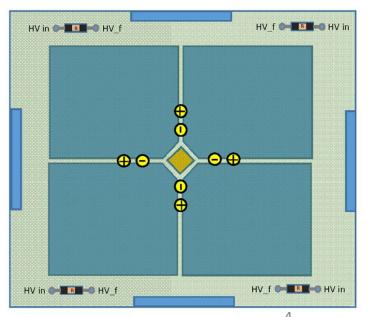

### Isochronous Signal Lines to the Penn ASIC

The Penn ASIC will collect the signals at one corner of the  $16 \times 16 \text{ mm}^2$  footprint of the tiled APD layout.

This gives us an opportunity to reduce the time walk by making the signal lines isochronous (equal length) from the "pins" along one edge of the footprint over to the input pad of the

ASIC.