# The ATLAS High Granularity Timing Detector for HL-LHC

L. Serin (CNRS/IN2P3/LAL)

Institutes involved in HGTD: CERN, LPNHE, LAL, Omega (France), Mainz, Giessen (Germany), Casablanca (Morocco), IFAE, CNM (Spain), JSI (Slovenia), KTH (Sweden), Sinica Academia, National Tsing-Hua University (Taiwan), BNL, Stony Brook, Iowa, Ohio, SMU, SLAC, UCSC (US), JINR (Russia) +....

Most of the material is from the ATLAS HGTD TP to be made public mid June

#### **Outline**

- ATLAS phase II and Motivation for the timing detector

- Detector requirements

- Sensors R&D

- Electronics R&D

- Clock distribution and t<sub>0</sub> calibration

- Layout design and expected performance

- Conclusion

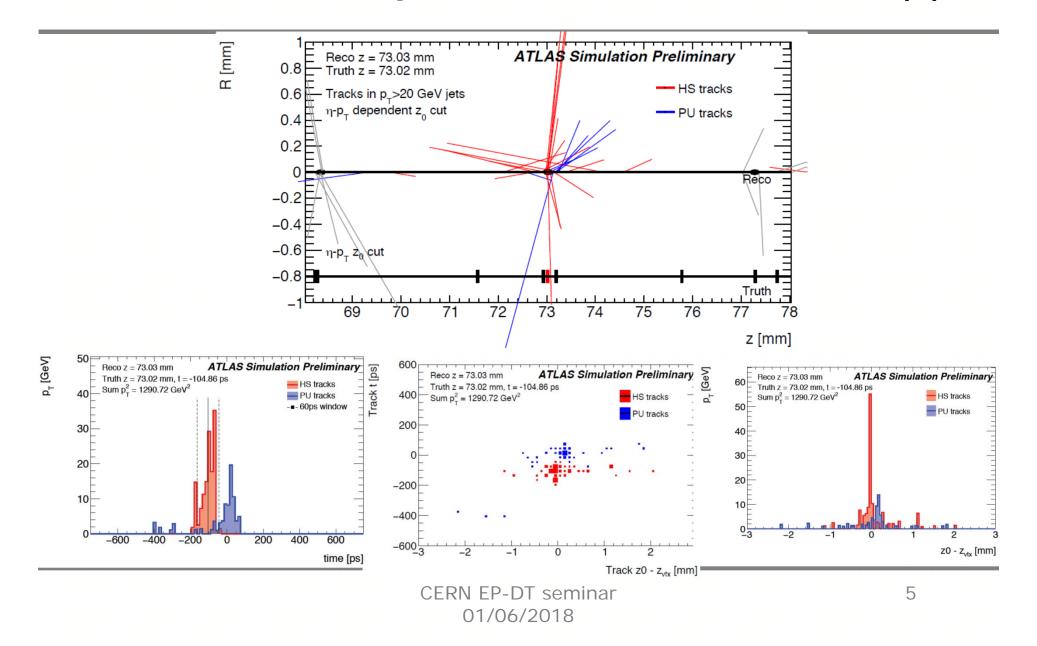

### Motivation for precise time measurements

#### HL-LHC:

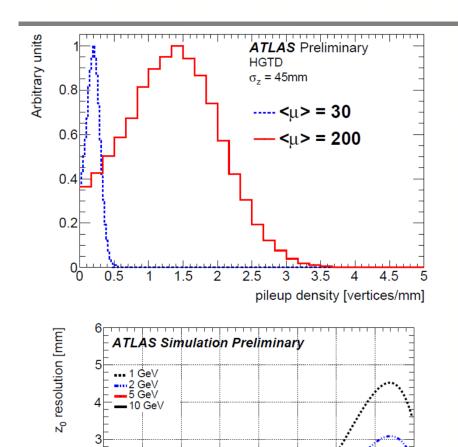

- expect  $<\mu> = 200$

- Average vertex density 1.8 vtx/mm  $z_0$  resolution increases with  $\eta$  and several vertices can be merged

- Degradation of performance at large η critical region for VBF signals

Loss also for lepton isolation and b tagging

### Motivation for precise time measurements (2)

### Motivation for precise time measurements (2)

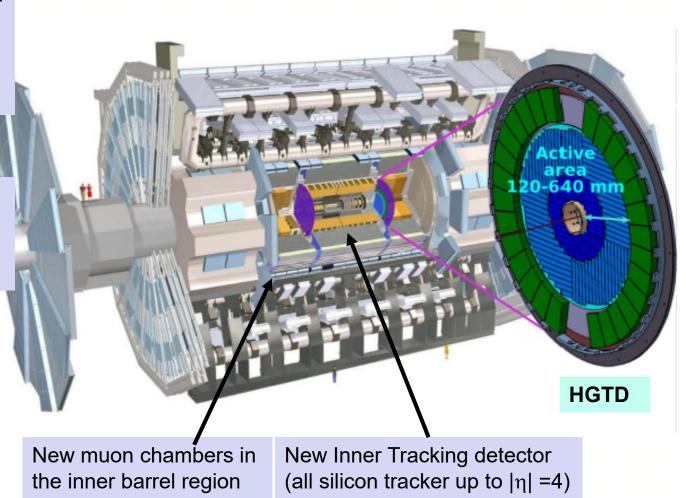

### ATLAS Phase II upgrade

#### **Upgraded Trigger and Data** Acquisition System:

- L0 @1 MHz

- Improved High Level Trigger

#### Electronics Upgrade:

- Lar calorimeter

- Tile calorimeter

- Muon system

#### Options:

- High  $\eta$  muon tagger

- Forward detector incl. **luminosity**

### **Detector Requirements**

The detector is quite constrained by the space available and the harsh environment while willing to reach excellent time resolution for mip track

#### → Low Gain Avalanche Diode Technology sensors

| Pseudorapidity coverage        | $2.4 <  \eta  < 4.0$          |

|--------------------------------|-------------------------------|

| Thickness in z                 | 75 mm (+50 mm moderator)      |

| Position of active layers in z | 3435  mm < z < 3485  mm       |

| Radial extension:              |                               |

| Total                          | 110  mm < R < 1000  mm        |

| Active area                    | 120  mm < R < 640  mm         |

| Time resolution per track      | 30 ps                         |

| Number of hits per track:      |                               |

| $2.4 <  \eta  < 3.1$           | 2                             |

| $3.1 <  \eta  < 4.0$           | 3                             |

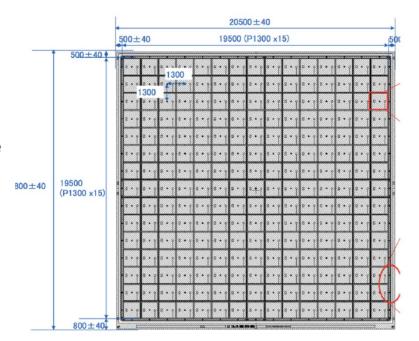

| Pixel size                     | $1.3 \times 1.3 \text{ mm}^2$ |

| Number of channels             | 3.54M                         |

| Active area                    | 6.3 m <sup>2</sup>            |

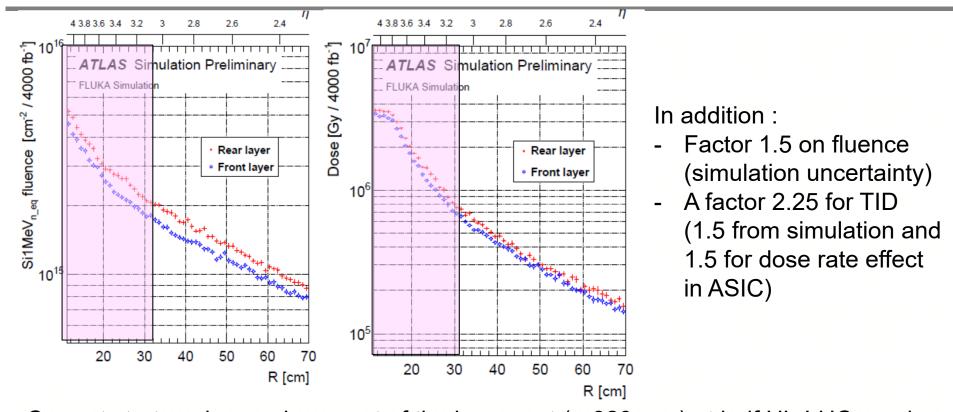

#### **Radiation levels in HGTD**

Current strategy is a replacement of the inner part (r<320 mm) at half HL-LHC running period:

max doses r < 320 mm 3.7  $10^{15} \text{ neq /cm}^2 \text{ and 4.1 MGy}$

r > 320 mm 3.0  $10^{15} \text{ neq}/\text{cm}^2 \text{ and } 1.6 \text{ MGy}$

#### Time resolution

#### **Total time resolution per hit:**

$$\sigma_{\text{total}}^2 = \sigma_{\text{L}}^2 + \sigma_{\text{elec}}^2 + \sigma_{\text{clock}}^2$$

#### Sensor R&D:

- Thickness, pad size, doping

- Radiation hardness (Ga, C spray..)

#### Electronics R&D:

- Dedicated ASIC

- Jitter & time walk

- Radiation hardness

- Power dissipation

$$\sigma_{\text{Jitter}} = \frac{N}{(dV/dt)} \simeq \frac{t_{\text{rise}}}{(S/N)}$$

Total time resolution per track  $\sigma(\text{track}) = \sigma(\text{hit}) / \sqrt{N_{\text{hits}}}$

Clock distribution (CERN working group) t0 calibration

goal < 30 ps

Optimise the number of hits per track

### **Sensors R&D activity**

with strong interaction with RD50 and some CMS colleagues

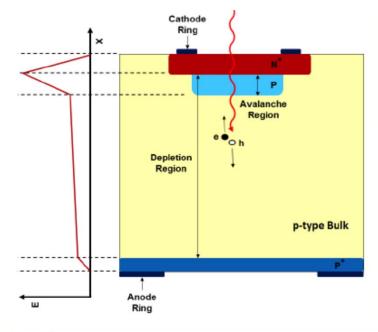

### **LGAD** first principles

-8 · · · Primary e+ h -7 Gain e+ h -6 -5 Current [µA] a) -2 0.0 0.2 0.4 0.6 0.8 1.0 Time [ns]

Low Gain Avalanche Diode pioneered by CNM.

Now produced by HPK and FBK with similar performance (except breakdown values)

BNL and Micro in near future

A lot of work also done within RD50

Gain (charge ratio of LGAD/diode) : (→ S/N)

- moderate gain (10-50) provided by thin highly doped avalanche region (a few μm with high electrical field, ~a few 100 kV/cm)

- depend on doping density

- independent of sensor thickness

Signal speed :  $(\rightarrow t_{rise})$

- Not very fast, rise time around 0.5-0.6 ns

- Rise time and duration depends on sensor thickness

N EP-DT seminar 01/06/2018

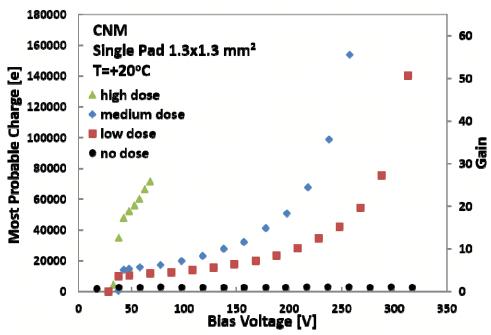

### Gain versus bias voltage

#### varying temperature

Breakdown voltage before irradiation quite sensitive to doping level

$(2.0, 1.9, 1.8 \ 10^{13} \ cm^{-2})$

→ gain of 20 reached easily

Operate at low temperature (target in ATLAS near –30 °c)

- → Gain x 2-3

- → Reduce operation voltage

CERN EP-DT seminar o1/06/2018 irradiation

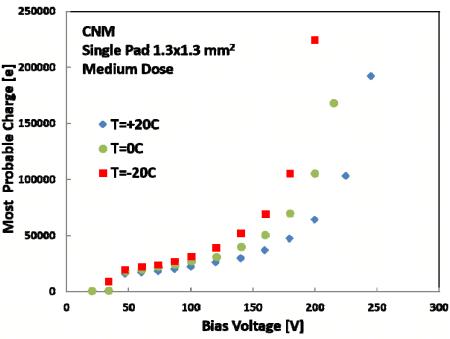

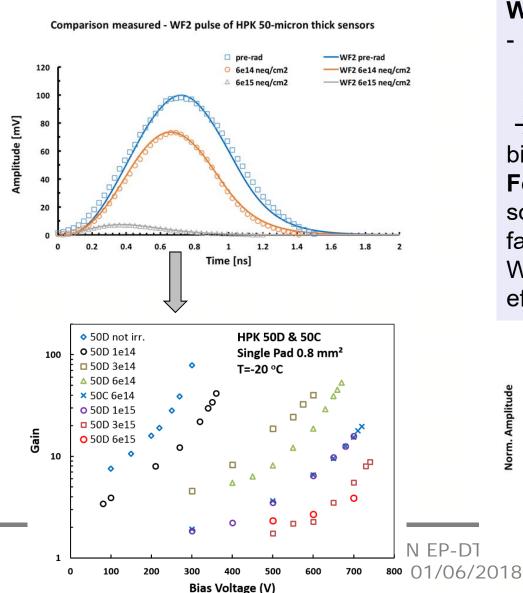

### Time resolution versus gain

Similar time resolution for CNM/HPK with ultimate time resolution of 30 ps for 50  $\mu$ m thickness, limited by "Landau" term

(measurements done with discrete, quite power dissipative, electronics sampling the signal (no TDC);

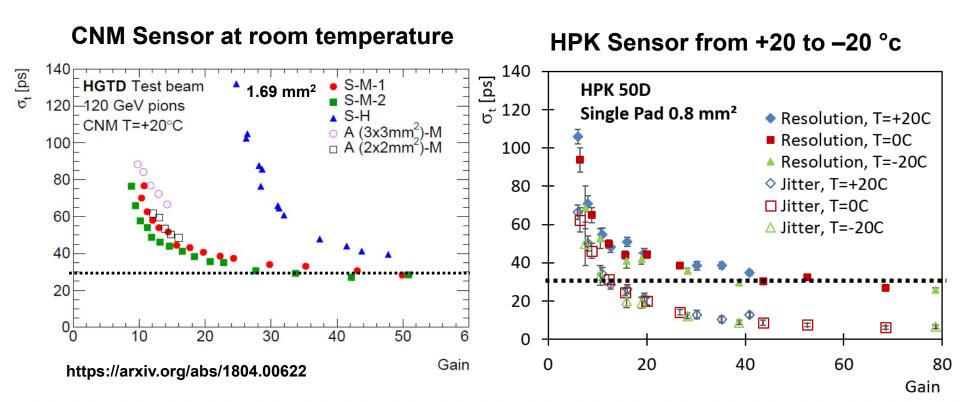

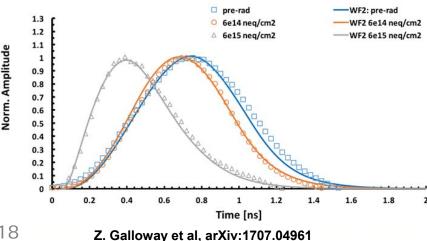

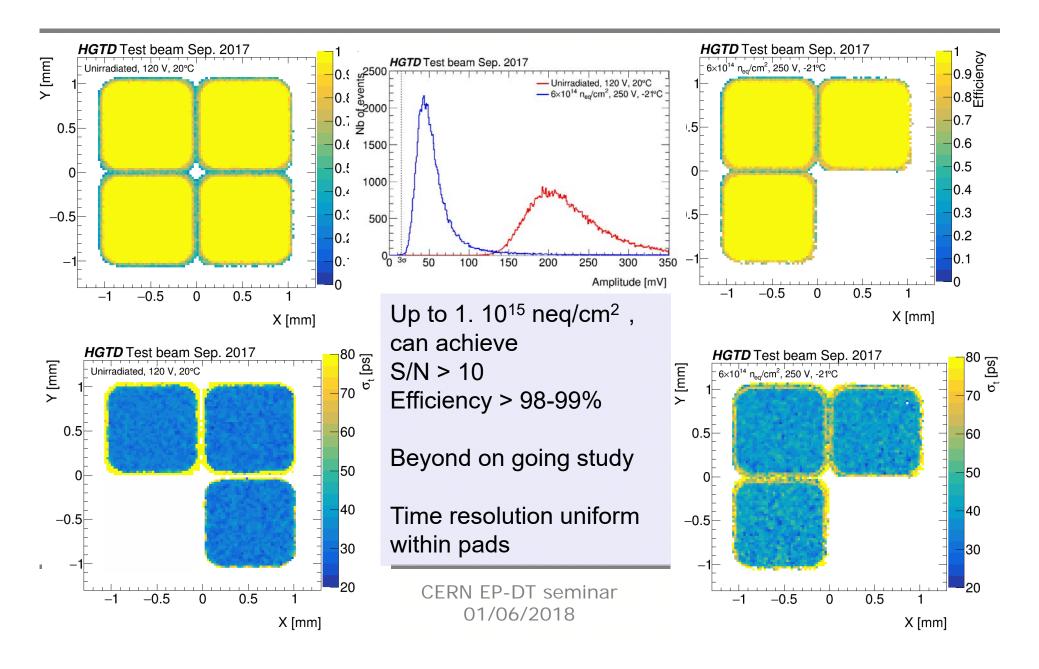

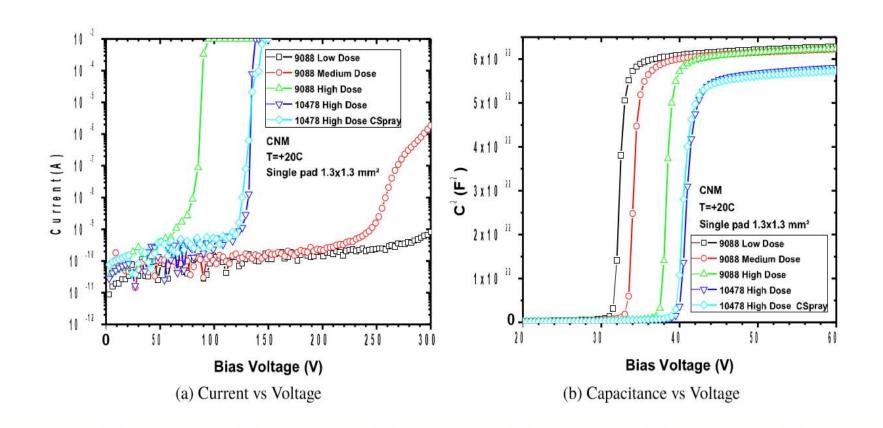

### Sensors gain with irradiation

#### With irradiation up to 1.10<sup>15</sup> neq/cm<sup>2</sup>

- Degradation of gain due to loss of effective doping in avalanche region, slightly faster signals

- → partially mitigating by increasing bias voltage

For fluence > 1.10<sup>15</sup> neq/cm<sup>2</sup> still some gain from the bulk region, and faster signal

With proton irradiation, slightly smaller effect

Comparison measured - WF2 pulse of HPK 50D 50-micron thick sensors

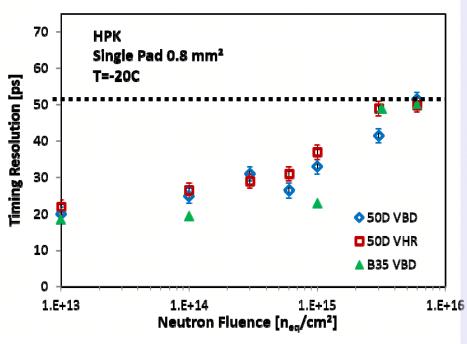

#### Sensors time resolution with irradiation

Time resolution smaller than 50 ps up to ~5. 10<sup>15</sup> neq/cm<sup>2</sup> with bias voltage (VHR) 10 % below breakdown voltage (VBD)

#### 35 µm thickness:

- a bit better than 50 μm below 1 10<sup>15</sup> neq/cm<sup>2,</sup> but similar at high fluence

- Smaller operating voltage

- But larger capacitance will make hard to achieve this performance with ASIC

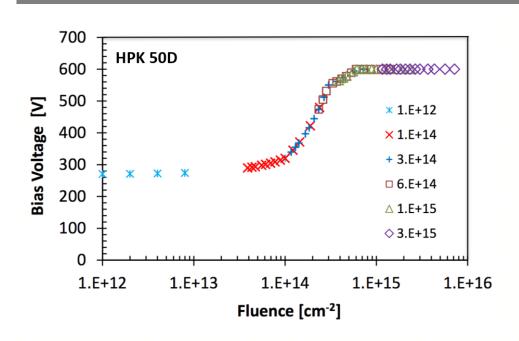

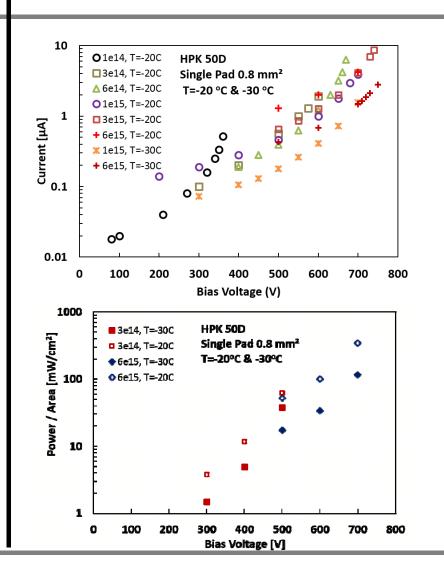

### Bias voltage operation

### Leakage current

Bias voltage to be adjusted as function of time (fluence) monitored by TOT and leakage current measurement

In current design, individual bias voltage per sensor (2 cm along X or Y direction)

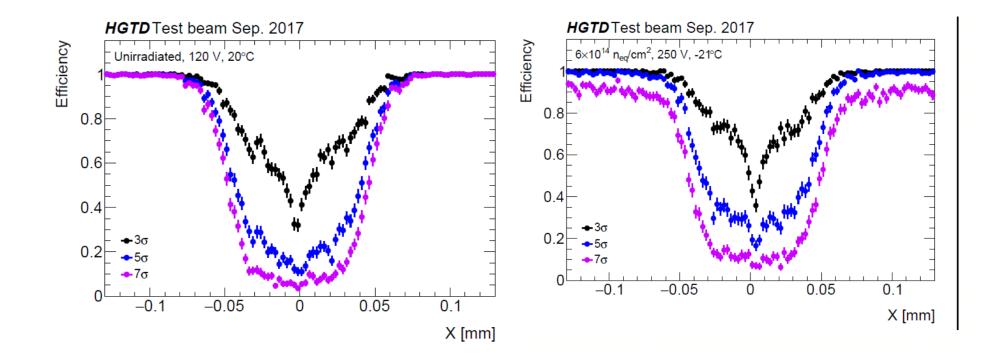

### **Preliminary pad array measurements**

### Main sensors R&D in 2018/2019

Test of sensors with Carbon spray in the bulk

Production of similar sensors structure and arrays (up to 2x2 cm<sup>2</sup>) by CNM and HPK

Optimisation of fill factor (inter pad distance from  $50 \rightarrow 100 \mu m$ )

Integrated sensor + ASIC measurements

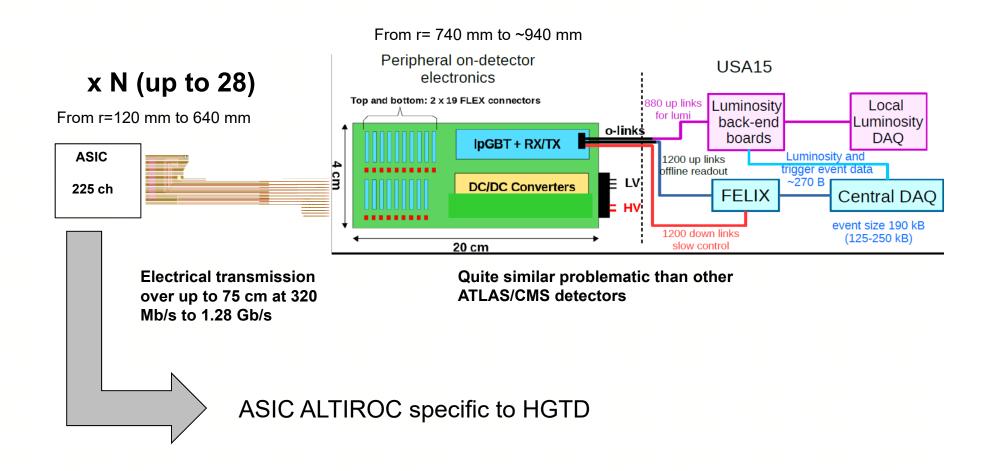

# **Electronics R&D activity**

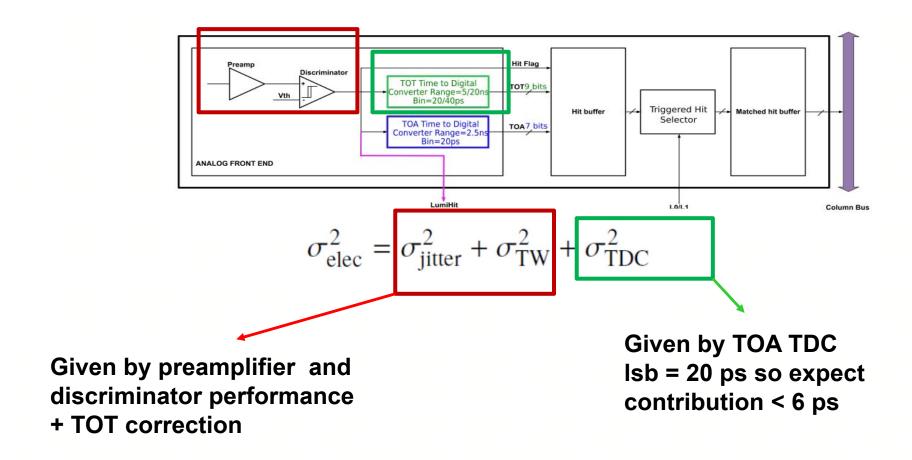

#### **Electronics read- out overview**

### **ASIC** requirements

| Pad size                                  | $1.3 \times 1.3 \text{ mm}^2$                                                 |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------|--|--|

| Detector capacitance                      | 3.4 pF                                                                        |  |  |

| TID and neutron fluence                   | Inner region: $4.1 \mathrm{MGy} 3.7 \times 10^{15} \mathrm{n_{eq}/cm^2}$      |  |  |

|                                           | Outer region: 1.6 MGy, $3.0 \times 10^{15}  \text{n}_{\text{eq}}/\text{cm}^2$ |  |  |

| Number of channels/ASIC                   | 225                                                                           |  |  |

| Collected charge (1 MIP) at gain=20       | 9.2 fC                                                                        |  |  |

| Dynamic range                             | 1-20 MIPs                                                                     |  |  |

| (preamplifier+discr.) jitter at gain = 20 | < 20 ps                                                                       |  |  |

| Time walk contribution                    | < 10 ps                                                                       |  |  |

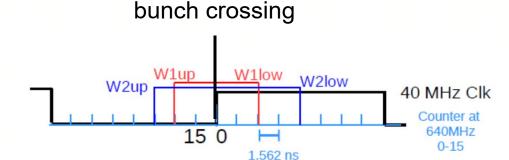

| TDC binning                               | 20 ps (TOA, TZ TOT), 40 ps (VA TOT)                                           |  |  |

| TDC range                                 | 2.5 ns (TOA), 5 ns (TZ TOT), 10 ns (VA TOT)                                   |  |  |

| Number of bits / hit                      | 7 for TOA and 9 for TOT                                                       |  |  |

| Luminosity counters per ASIC              | 7 bits (sum) + 5 bits (outside window)                                        |  |  |

| Total power per area (ASIC)               | <300 mW/cm <sup>2</sup> (<1.2 W)                                              |  |  |

| e-link driver bandwidth                   | 320 Mb/s, 640 Mb/s or 1.28 Gb/s                                               |  |  |

| Latency for L0/L1 triggering              | 10/35 μs                                                                      |  |  |

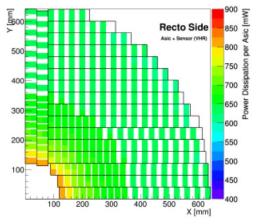

Challenging radiation level, choose TSMC 130 nm CMOS

Challenging timing resolution for small charge

Keep acceptable power dissipation for CO2 cooling

Cope with both ATLAS trigger scheme

And quite reduced time for ASIC R&D...

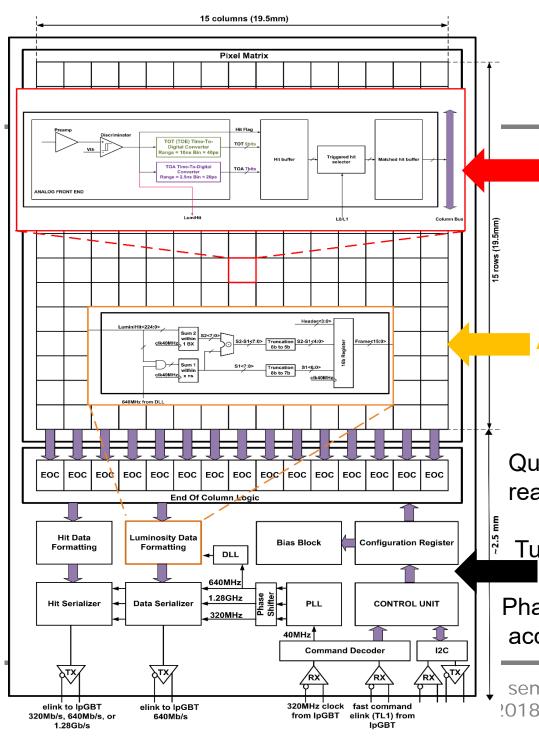

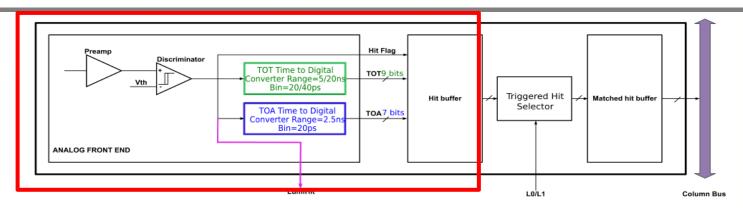

### **ASIC** architecture

225 pixel read-out channels (at prototype level)

A luminosity data formatting block

Quite standard off-pixel detector matrix read-out (still at design phase)

Tuneable speed serializers

Phase shifter for the clock with ~100 ps accuracy

seminar 2018

#### Pixel architecture

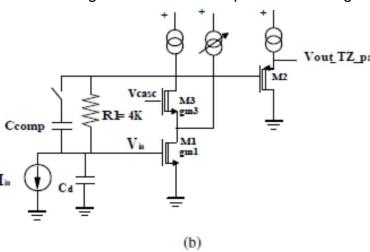

### Preamplifier design

$$\sigma_{jitter} = \frac{N}{dV/dt} = \frac{e_n C_d}{Q_{in}} \sqrt{\frac{t r_{\rm a}^2 + t_d^2}{2t r_{\rm a}}} \ = \frac{C_T}{Q_{in}} \sqrt{\frac{2k T t_s}{g_m}} \,, \label{eq:sigma}$$

- $\rightarrow$  No need of infinitely fast preamplifier. Preamplifier rise-time (tr<sub>a</sub>) matched to LGAD rise-time t<sub>d</sub>: tr<sub>a</sub> = t<sub>d</sub> = t<sub>s</sub> in the range 0.5-1 ns

- → Optimise t<sub>s</sub> and g<sub>m</sub> (using relatively large transistors and currents)

Pseudo-Trans-impedance amplifier (TZ) similar as Test Beam design with discrete components and larger current

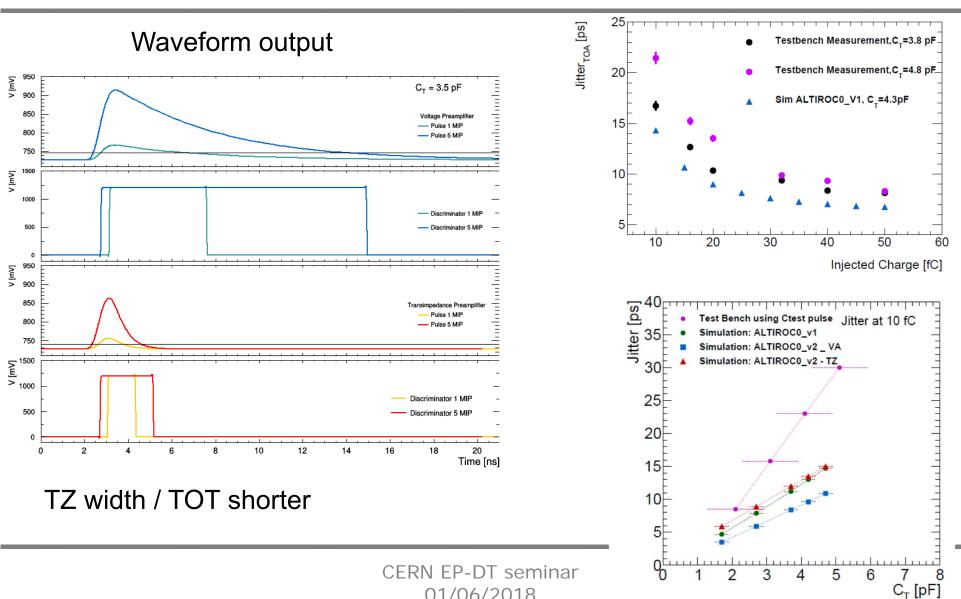

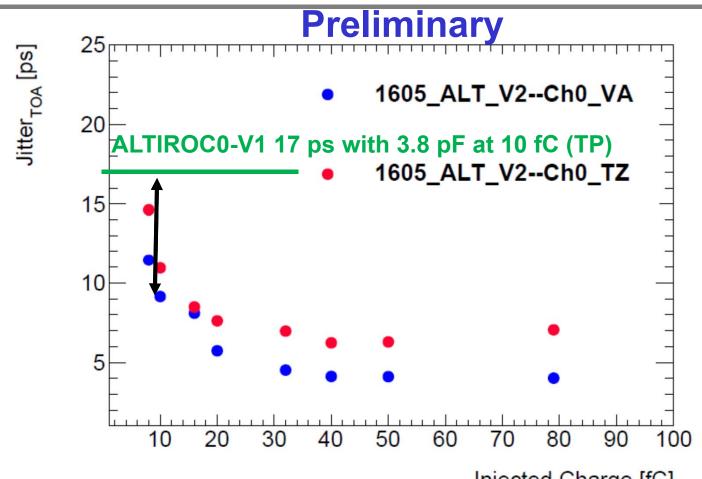

### Preamplifier performance

### **ALTIROC0-V2: VERY preliminary measurements**

Injected Charge [fC]

On going test bench measurements. Mid June sensor bump bonded and End June

beam test at CERN

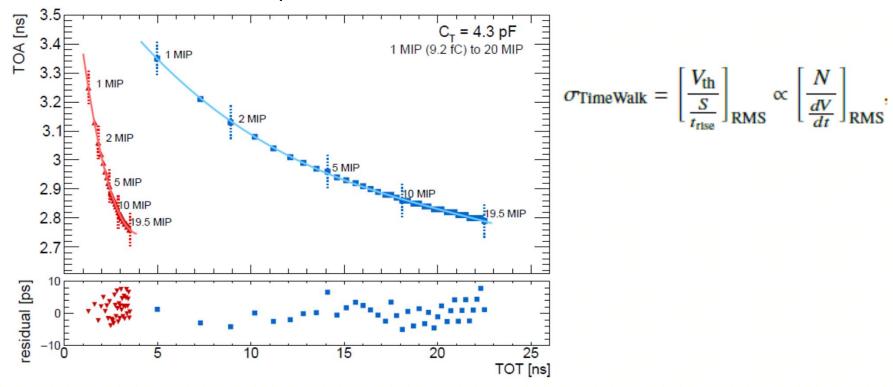

### **Time Walk correction**

Use TOT as estimator of amplitude to correct for time walk effect

After correction, peak to peak variation < 20 ps so contribution to < 10 ps to resolution TZ fast dependence implies a 20 ps lsb for the TOT measurements, while VA can be 40 (80) ps

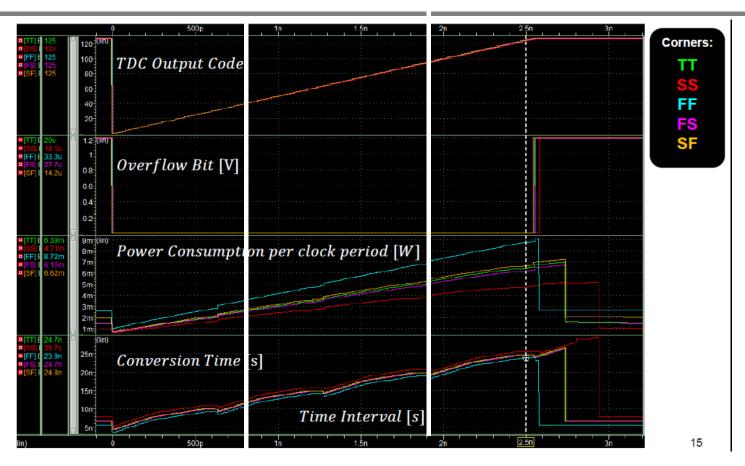

### Time to Digital Converter (TDC) for TOA

Vernier delay configuration with two delay lines:

- Time resolution (20 ps) = difference in the delay of the cells in each line **slow** (140 ps) and **fast** (120 ps) lines

- Time measurement (TOA) only over 2.5 ns window centered on bunch crossing TOA given by the number of stage needed to have the STOP to surpass the START

- No power consumption if not hit.

TOT TDC made of a Coarse delay line + TOA TDC

### Time to Digital Converter (TDC)

Most of the hit in time within central window → power consumption 5 mW x occupancy Conversion still to be optimized to stay within 25 ns

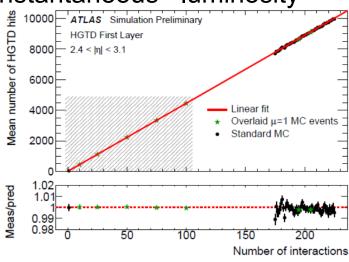

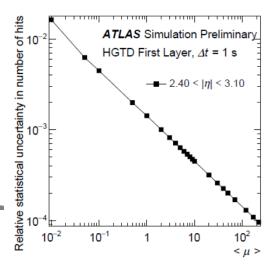

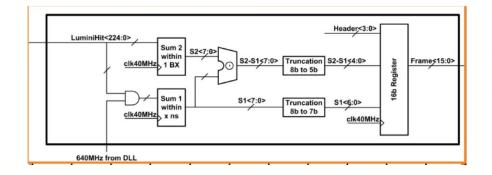

### **Luminosity counters**

HGTD can easily provide an instantaneous luminosity

For each ASIC,

- compute number of hits in two windows centered on bunch crossing

- transmit in time and out-time numbers of hits at each bunch crossing

#### **ALTIROC1**

25 channels chip with preamplifier (VA or TZ) + discriminator + TOA and TOT (TDC) and local memory

Include prototype of final clock distribution in ASIC for 16 channels

Layout finished, post simulation ongoing Submission on June 13 th Might include an independent block with phase shifter if ready

## Clock distribution and t<sub>0</sub> calibration

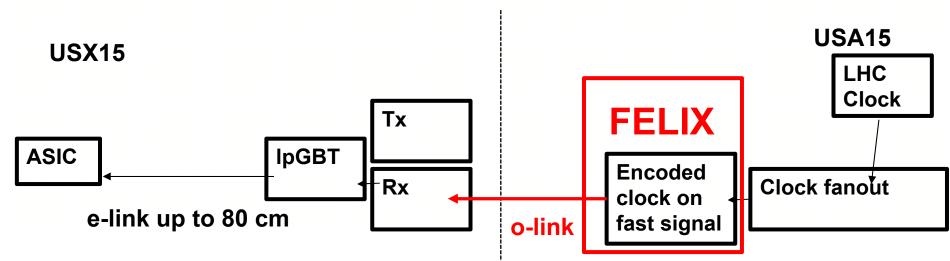

### **Clock distribution to ASIC: jitter**

Baseline design is to transmit the clock encoded through the IpGBT

- → Clock contribution to time resolution relies on expected lpGBT jitter < 5 ps and FELIX contribution : total < 10 ps ?</p>

- → Might clean it in ASIC (PLL)

- → Providing a clock directly through dedicated links quite difficult for services

Work started within the ATLAS/CMS common working group set-up by CERN-EP-ESE-BE (S. Baron)

#### Clock distribution to ASIC: wander

Phase shifter in ASIC only used to align coarsely the measurement window (~100 ps accuracy)

t<sub>0</sub> of each channel needs to be calibrated to a few ps:

- different path length for signal, time of flight → calibration signals

- "Low frequency" clock phase variation with time/temperature → wander

- → use data to compute/correct online/offline the possible t<sub>0</sub> variations

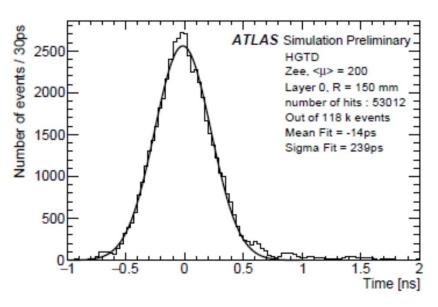

#### T0 calibration with data

Inclusive hit time distribution in a pixel: rms 240 ps

$\rightarrow$  Can measured t<sub>0</sub> of pixel to better than 5 ps with 10000 hits

Taken into account occupancy, it corresponds to 10<sup>5</sup> events at inner radius and 10<sup>6</sup> events at higher radius

| In Felix board dat       | a at 1 MHz, | offline data at 10 kHz |

|--------------------------|-------------|------------------------|

| Inner radius per channel | 0.1 s       | 10 s                   |

| Outer radius per channel | 1s          | 100 ps                 |

| Per ASIC (inner/outer)   | 0.4/4 ms    |                        |

→ Could correct low frequency variation up few kHz frequency

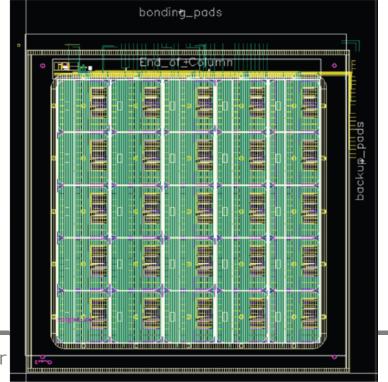

# Layout optimisation and design

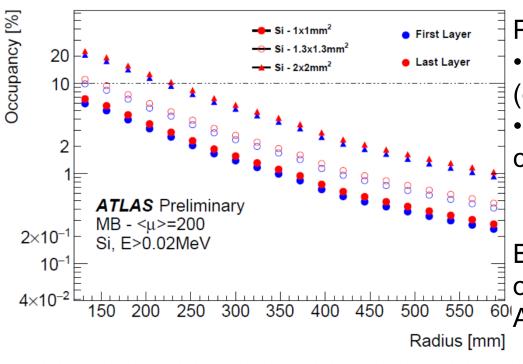

# Sensor pad size

Pad size is a trade-off between

- Occupancy and time resolution (capacitance) → small pads

- Efficiency (fill factor) and channel density (power consumption)

→ large pads

Baseline is a unique sensor pad size of 1.3 x 1.3 mm<sup>2</sup>

All sensors identical (4x2 or 4x4 cm<sup>2</sup>)

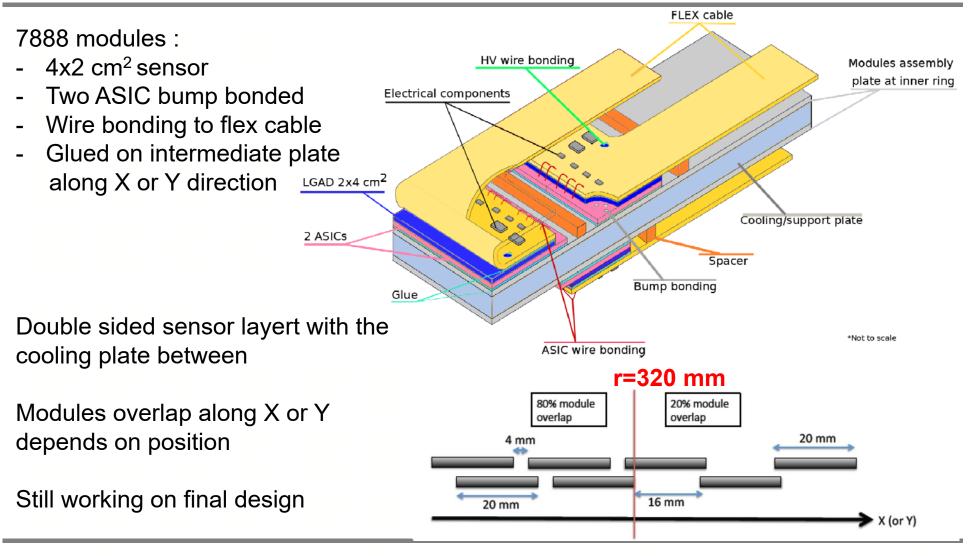

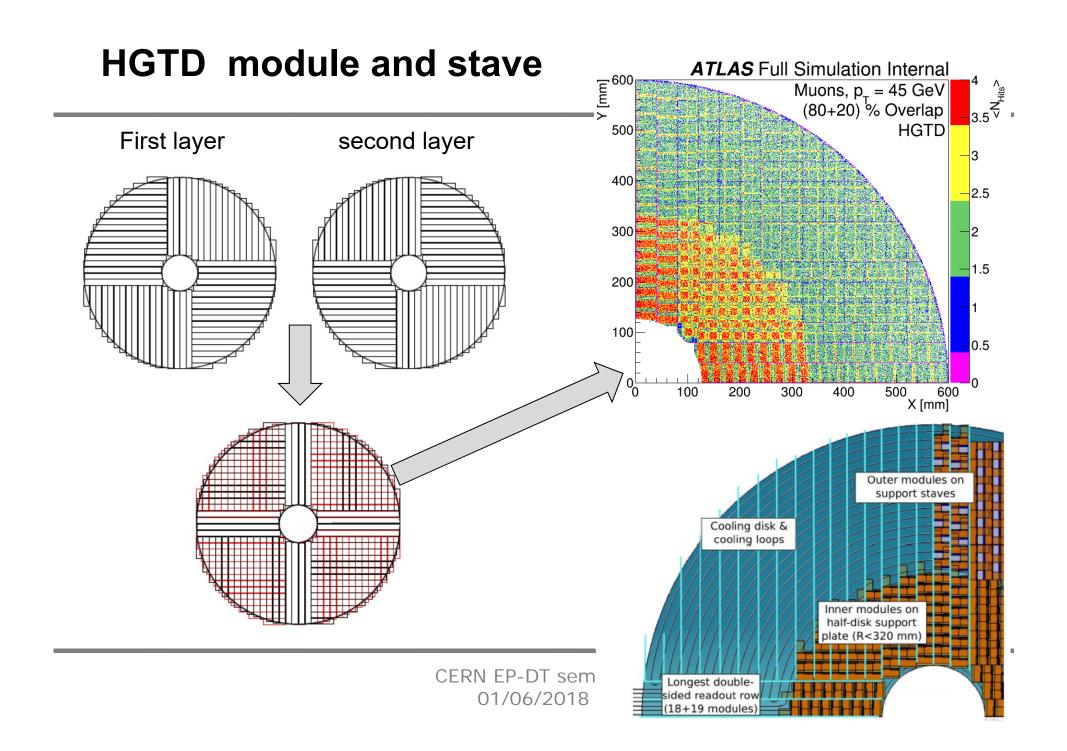

### **HGTD** Module and stave

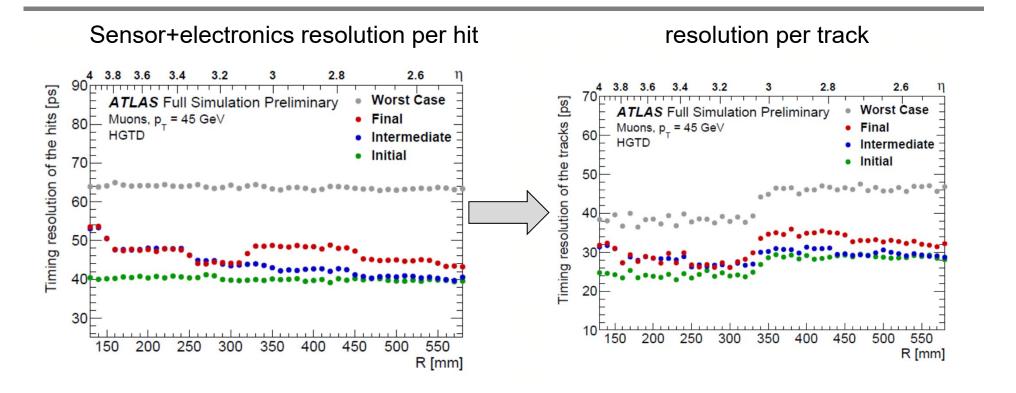

## Summary expected time resolution

Modules at r < 320 mm replaced at middle of HL-LHC integrated luminosity Compensate at inner radius time resolution by increasing number of hits.

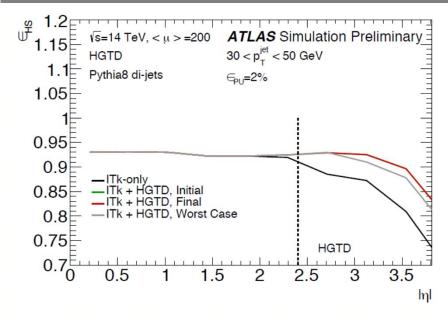

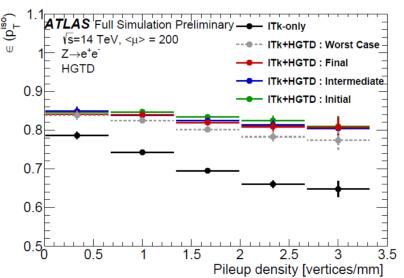

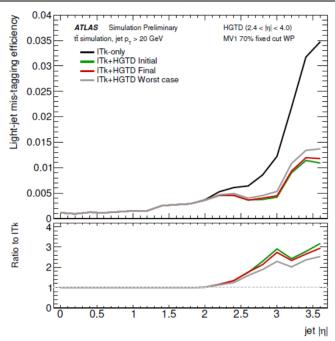

## **Expected performance**

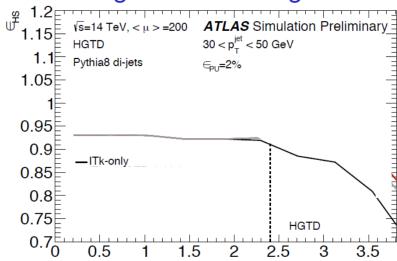

#### Using HGTD in forward region :

- restore similar performance to central region (ITk only)

- small degradation w/ pileup density

- → Make more robust performance Impact on physics channels (VBF Higgs, tH) expected about 10-15 %

### Conclusion

Providing 30 ps per track resolution in the HL-LHC environment is quite challenging ..... but looks achievable.

R&D started in ATLAS about only two years ago but a lot progress/results achieved

Last review with LHCC on Technical Proposal this Monday

→ Hope green light in these days for a TDR by March 2019

2018→2020 R&D to finalize HGTD design 2021→2024/25 : production / construction with stave 0 in 2021

→ Installation in June/July 2025

# **BACK-UP**

## Sensor parameters : IV and CV curves

# **Power dissipation**

| Component            | Nominal [µW] |  |

|----------------------|--------------|--|

| Preamplifier         | 462          |  |

| Discriminator+DAC    | 375          |  |

| TDC TOT (10ns/40ps)  | 500          |  |

| TDC TOA (2.5ns/20ps) | 405          |  |

| Local Memory         | 920          |  |

| Total Pixel          | 2666         |  |

Table 11: Single pixel average readout power consumption. For the TDC and local memory (full buffer option), a 10% occupancy factor is applied.

(a) Front view

| Component                          | Power consumption                                        | Total [kW] | Maximal [kW] |

|------------------------------------|----------------------------------------------------------|------------|--------------|

| Sensor                             | < 30 mW/cm <sup>2</sup>                                  | 1.9        | 1.9          |

| ASIC                               | $<175 \text{ mW/cm}^2$                                   | 8.5        | 12.8         |

| Flex cable                         | < 100 mW/flex                                            | 0.5        | 1.1          |

| HGTD cold vessel heaters           | $75 \text{ W/m}^2 - 175 \text{ W/m}^2$                   | 0.33       | 0.33         |

| EC calorimeter cryostat heaters    | $120 \text{ W/m}^2$ , $50\%$ up to $R = 1600 \text{ mm}$ | < 0.6      | 0.6          |

| Peripheral on-detector electronics | dominated by DC/DC converter                             | 3.25       | 4.9          |

| Total for CO <sub>2</sub> cooling  |                                                          | 15.1       | 21.6         |

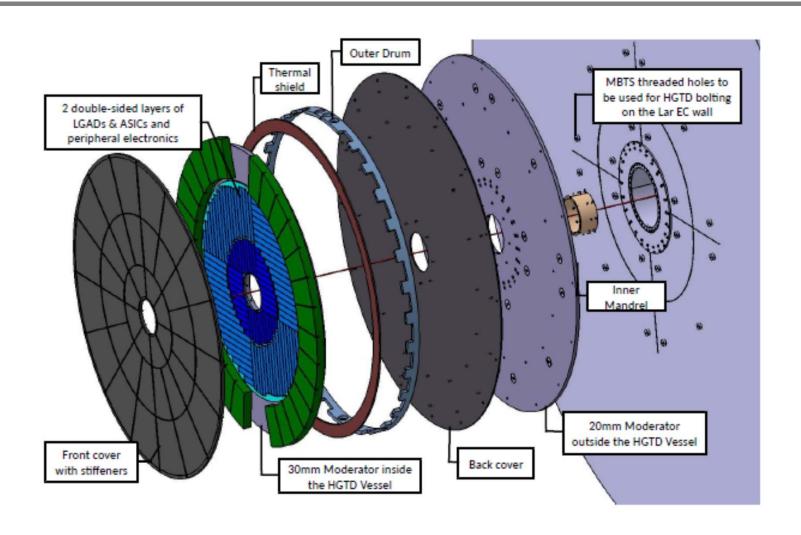

# **HGTGD** exploded view

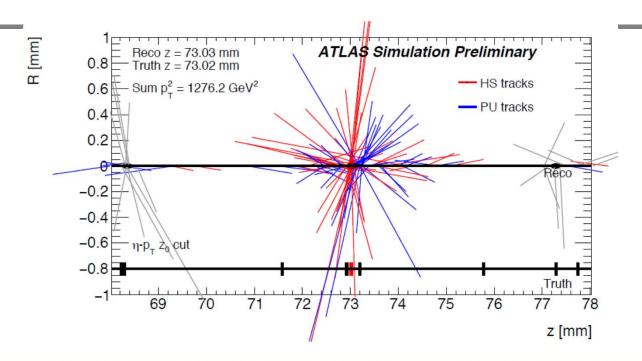

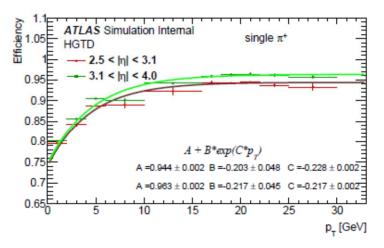

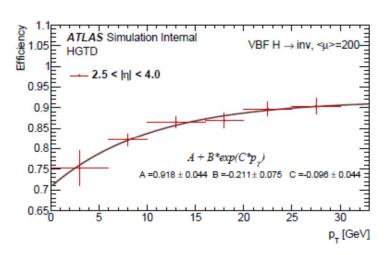

# Track matching efficiency

(a) Efficiency for matching tracks to at least one HGTD pixel. (b) Estimated efficiency for assigning the correct time to tracks.

# Inter pad distance (fill factor)